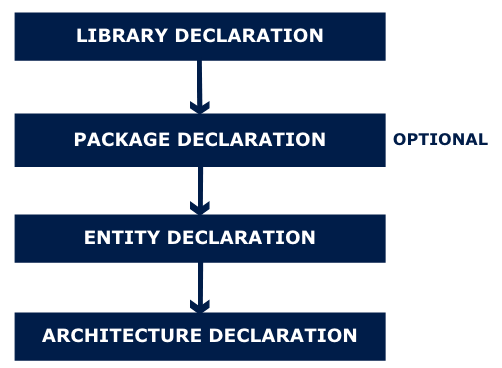

VHDL का Default Structure (Easy Guide)

1. Library Declaration (लाइब्रेरी चुनना)

Library Declaration (सामग्री चुनना) VHDL में हर चीज़ के लिए पहले से कुछ definitions बनी होती हैं, जैसे std_logic signal, arithmetic operations आदि।

इनको use करने के लिए शुरुआत में libraries लिखी जाती हैं:

2. Entity Declaration (Black Box का बाहरी हिस्सा)

Entity को आप एक black box मान सकते हैं।

-

इसके generics parameters की तरह हैं (जैसे width, size)।

-

इसके ports input-output pins की तरह हैं।

यहाँ entity सिर्फ box के बाहर की wires define करती है – अंदर क्या हो रहा है, वो नहीं बताती।

3. Architecture Declaration (Black Box का अंदरूनी logic)

-

अब architecture में हम लिखते हैं कि box के अंदर क्या logic लगा है।

-

इसमें signals, constants, FSM, counters सब define किए जाते हैं।

जब भी VHDL code लिखते हैं, हम हमेशा यही 3 step follow करते हैं:

Library → Entity → Architecture

आइये इसे हम अपने असिंक्रोन्स उप/डाउन काउंटर से समझते है

VHDL Counter Example (Load, Enable, Up/Down के साथ)

सबसे ऊपर हमें standard libraries use करनी होती हैं:

1. Library Declaration (लाइब्रेरी चुनना)

VHDL

LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

USE IEEE.numeric_std.all;

-

std_logic → digital signals के लिए

-

numeric_std → arithmetic operations (जैसे +, -) के लिए

2. Entity Declaration (Black Box का बाहरी हिस्सा)

Entity में हम inputs और outputs declare करते हैं:

VHDL

ENTITY counter IS

PORT (

clock : IN std_logic; -- clock signal

rst : IN std_logic; -- reset (active low)

ENABLE : IN std_logic; -- enable counting

LOAD : IN std_logic; -- load counter_in into counter

UP_DOWN : IN std_logic; -- 1 = up, 0 = down

counter_in : IN std_logic_vector(3 DOWNTO 0); -- load value

counter_out : OUT std_logic_vector(3 DOWNTO 0) -- current counter output

);

END counter;

समझिए:

-

clock → गिनती clock edge पर होती है।

-

rst → reset signal (yaha active low hai, यानी 0 par reset karega)।

-

ENABLE → enable = 1 होने पर ही counter काम करेगा।

-

LOAD → input value को counter में डालने के लिए।

-

UP_DOWN → गिनती की दिशा तय करता है (1 = ऊपर, 0 = नीचे)।

-

counter_in → load करने वाला value।

-

counter_out → output value।

3. Architecture (अंदर का logic)

अब हम define करते हैं कि अंदर क्या होगा:

VHDL

ARCHITECTURE behavioral OF counter IS

SIGNAL counter_out_tmp : unsigned(3 DOWNTO 0); -- unsigned for arithmetic

BEGIN

counter_proc : PROCESS (rst, clock)

BEGIN

IF (rst = '0') THEN

counter_out_tmp <= (OTHERS => '0'); -- reset to zero

ELSIF rising_edge(clock) THEN

IF (LOAD = '1') THEN

counter_out_tmp <= unsigned(counter_in); -- load value

ELSIF (ENABLE = '1') THEN

IF (UP_DOWN = '1') THEN

counter_out_tmp <= counter_out_tmp + 1; -- count up

ELSE

counter_out_tmp <= counter_out_tmp - 1; -- count down

END IF;

END IF;

END IF;

END PROCESS;

counter_out <= std_logic_vector(counter_out_tmp); -- convert back

END behavioral;

समझिए:

-

Reset (rst=0) → counter = 0

-

हर clock rising edge पर:

-

अगर LOAD=1 → counter_in load होगा

-

वरना अगर ENABLE=1:

-

UP_DOWN=1 → counter बढ़ेगा

-

UP_DOWN=0 → counter घटेगा

-

-

यानि यह counter reset हो सकता है, load कर सकता है, enable/disable हो सकता है और up/down count कर सकता है।

Extra component of File:

Now we will understand how a package is created from this, let's see

पैकेज डिक्लेरेशन :

VHDL में package बनाने का मतलब है कई सारी चीज़ों को एक जगह इकट्ठा करना, जैसे:

-

Constants (स्थिर मान)

-

Types / Subtypes (डेटा प्रकार)

-

Functions / Procedures (फंक्शन और प्रोसीजर्स)

-

Reusable Components (Modules/Entities) (पुन: उपयोग योग्य घटक)

और जो चीज़ आपके डिज़ाइन में आवश्यक है, उसे आप उस package से उपयोग कर सकते हैं।

सही अर्थ में, package एक डिब्बा है जिसमें पुन: उपयोग योग्य और ज़रूरी चीज़ें संग्रहित की जाती हैं, ताकि बार-बार अलग-अलग फाइल में न लिखना पड़े।

VHDL में Package क्यों use करते हैं?

-

VHDL में package इसलिए use किया जाता है ताकि हम बार-बार लिखने वाले common code को reuse कर सकें।

-

हर design file में वही चीज़ें दुबारा लिखने की बजाय, हम उन्हें एक बार package में डाल देते हैं।

-

Package के अंदर हम लिखते हैं:

-

constants

-

types

-

functions/procedures

-

component declaration (entity का नक्शा)

-

फिर किसी भी RTL file में बस ये लिखना होता है:

use work.my_package.all;

और हम उस design या definitions को use कर सकते हैं।

इसलिए अगर हमें एक ही design दूसरी RTL file में use करना हो, तो हम उसका component declaration package में डालते हैं और बाद में उसे instantiate कर लेते हैं।

Package = VHDL में code को बार-बार reuse करने का तरीका।

VHDL Counter को बार-बार इस्तेमाल करना

VHDL में आप पूरा entity + architecture package में नहीं रख सकते

Package सिर्फ इन चीज़ों के लिए होता है:

-

Constants

-

Types

-

Functions/Procedures

-

Component Declaration (entity का "नक्शा")

So the correct way is:

Step 1: Counter का कोड अलग file में लिखो

Counter का पूरा कोड (entity + architecture) अपनी file counter.vhd में रखो।

VHDL

-- counter.vhd

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity counter is

port (

clock : in std_logic;

rst : in std_logic;

ENABLE : in std_logic;

LOAD : in std_logic;

UP_DOWN : in std_logic;

counter_in : in std_logic_vector(3 downto 0);

counter_out : out std_logic_vector(3 downto 0)

);

end counter;

architecture behavioral of counter is

signal counter_out_tmp : unsigned(3 downto 0);

begin

process (rst, clock)

begin

if (rst = '0') then

counter_out_tmp <= (others => '0');

elsif rising_edge(clock) then

if (LOAD = '1') then

counter_out_tmp <= unsigned(counter_in);

elsif (ENABLE = '1') then

if (UP_DOWN = '1') then

counter_out_tmp <= counter_out_tmp + 1;

else

counter_out_tmp <= counter_out_tmp - 1;

end if;

end if;

end if;

end process;

counter_out <= std_logic_vector(counter_out_tmp);

end behavioral;

Step 2: Package बनाओ (component declaration के साथ)

अब एक package बनाओ, जैसे up_down_pkg.vhd

VHDL

-- up_down_pkg.vhd

library ieee;

use ieee.std_logic_1164.all;

package up_down_pkg is

component counter

port (

clock : in std_logic;

rst : in std_logic;

ENABLE : in std_logic;

LOAD : in std_logic;

UP_DOWN : in std_logic;

counter_in : in std_logic_vector(3 downto 0);

counter_out : out std_logic_vector(3 downto 0)

);

end component;

end package up_down_pkg;

ये package वैसा ही है जैसे C/C++ में header file होती है।

Step 3: किसी और design में use �करो

अब top.vhd file में इस package को use करके counter को instantiate करो:

VHDL

library ieee;

use ieee.std_logic_1164.all;

use work.up_down_pkg.all; -- import the package

entity top is

port (

clk : in std_logic;

rst : in std_logic;

q_out : out std_logic_vector(3 downto 0)

);

end top;

architecture rtl of top is

begin

u1: counter

port map (

clock => clk,

rst => rst,

ENABLE => '1',

LOAD => '0',

UP_DOWN => '1',

counter_in => "0000",

counter_out => q_out

);

end rtl;

यहाँ टॉप फाइल के अंदर उप/डाउन काउंटर को इंस्टांटिट या उसे किया जा रहा है जो की पोर्ट मैपिंग के द्वारा की जा रही है इसे आगे के लेक्टर्स में बताऊंगा , जब डिज़ाइन बहुत बड़ी हो और एक कॉम्पोनेन्ट को दूसरी डिज़ाइन में उसे use किया जाता है तो उसे पोर्ट मैप करते है

एक VHDL पैकेज में आप जितने चाहो उतने components रख सकते हो, जैसे constants, types, subtypes, functions, procedures, और reusable component declarations।

VHDL में कोई कठोर सीमा नहीं है, लेकिन practical सीमा आपके tool/compiler और design complexity पर निर्भर करती है।

बेहतर readability और reuse के लिए संबंधित components को एक साथ रखें, और बहुत बड़े पैकेज को छोटे-छोटे logical packages में विभाजित किया जा सकता है।

Important for Interview:

अभी तक आप को यह नहीं समझ आया होगा की लाइब्रेरी , इसका उसे और वर्क लाइब्रेरी क्या है।, आइये इसे समझते है

library ieee;

-

इसका मतलब है कि हम VHDL को बताते हैं कि हम एक स्टैंडर्ड लाइब्रेरी का उपयोग करना चाहते हैं।

-

ieee VHDL की स्टैंडर्ड लाइब्रेरी है, जो पहले से तैयार functions और types प्रदान करती है।

use ieee.std_logic_1164.all;

-

हम ieee लाइब्रेरी के std_logic_1164 पैकेज का उपयोग कर रहे हैं।

-

इस पैकेज में स्टैंडर्ड लॉजिक प्रकार होते हैं, जैसे std_logic और std_logic_vector।

-

ये प्रकार सिग्नल्स को दर्शाते हैं, जैसे 0, 1, अज्ञात (X), और हाई-इम्पीडेंस (Z)।

use work.up_down_pkg.all;

-

work का मतलब है वर्तमान प्रोजेक्ट/लाइब्रेरी।

-

up_down_pkg आपका या किसी और का बनाया हुआ पैकेज है, जिसमें constants, types या functions होते हैं।

-

all का मतलब है पैकेज की सभी चीज़ों का उपयोग करें।

यह इसलिए उपयोगी है ताकि आप एक ही कोड को कई फाइलों में बिना दोबारा लिखे उपयोग कर सकें।