11.1. Predefined Gate Primitives in Verilog: Complete Reference

Introduction

Verilog provides a comprehensive set of built-in gate primitives that represent fundamental logic gates and switches. These primitives are the building blocks of gate-level modeling and are essential for understanding how digital circuits are implemented in hardware.

Syntax:

primitive_type [#delay] instance_name (output, input1, input2, ...);

Example:

and and_gate1 (y, a, b); // 2-input AND gate

Characteristics:

- Pre-built: No need to define their behavior

- Instantiated: Used like modules with instance names

- Hardware-mapped: Directly correspond to physical gates

- Simulation models: Include timing and strength information

What You'll Learn:

- Complete reference of all Verilog gate primitives

- Syntax and usage of each primitive type

- Practical applications and examples

- Strength modeling and resolution

- Interview-focused concepts

- Industry best practices

Understanding gate primitives is crucial for:

- Writing gate-level netlists

- Understanding synthesizer output

- Post-synthesis simulation

- Low-level circuit design

11.1.1. Basic Logic Gates

1. AND Gate

Implements logical AND operation.

Truth Table:

Syntax:

and instance_name (output, input1, input2, ... inputN);

Examples:

Verilog

Applications:

- Enable signals

- Masking operations

- Control logic

2. OR Gate

Implements logical OR operation.

Truth Table:

Syntax:

or instance_name (output, input1, input2, ... inputN);

Examples:

Verilog

Applications:

- Combining signals

- Priority logic

- Status flags

3. NOT Gate (Inverter)

Implements logical NOT operation (inversion).

Truth Table:

Syntax:

not instance_name (output, input);

Examples:

Verilog

Applications:

- Signal inversion

- Complement generation

- Logic negation

4. NAND Gate

Implements logical NAND operation (NOT-AND).

Truth Table:

Syntax:

nand instance_name (output, input1, input2, ... inputN);

Examples:

Verilog

Special Properties:

- Universal gate (can implement any logic function)

- Commonly used in CMOS design

- Lower power than AND-NOT combination

NAND as Universal Gate:

Verilog

5. NOR Gate

Implements logical NOR operation (NOT-OR).

Truth Table:

Syntax:

nor instance_name (output, input1, input2, ... inputN);

Examples:

Verilog

Special Properties:

- Universal gate (can implement any logic function)

- Used in SR latches

- Common in memory design

NOR as Universal Gate:

Verilog

6. XOR Gate

Implements logical XOR (Exclusive-OR) operation.

Truth Table:

Syntax:

xor instance_name (output, input1, input2, ... inputN);

Examples:

Verilog

Applications:

- Half adder and full adder circuits

- Parity generation and checking

- Comparators

- Data encryption

Properties:

- Associative: A ⊕ B ⊕ C = (A ⊕ B) ⊕ C

- Commutative: A ⊕ B = B ⊕ A

- A ⊕ 0 = A

- A ⊕ 1 = A'

- A ⊕ A = 0

7. XNOR Gate

Implements logical XNOR (Exclusive-NOR) operation.

Truth Table:

Syntax:

xnor instance_name (output, input1, input2, ... inputN);

Examples:

Verilog

Applications:

- Equality comparison

- Even parity generation

- Error detection

11.1.2. Multi-Input Gates

All gates (except NOT) can have multiple inputs.

Example: 8-input AND gate

Verilog

11.1.3. Buffer and Inverter Primitives

1. BUF (Buffer)

Passes input to output without inversion.

Syntax:

buf instance_name (output, input);

Usage:

Verilog

Applications:

- Signal buffering

- Drive strength enhancement

- Fan-out management

- Delay insertion

2. NOT (Detailed)

Multiple Output Capability:

Verilog

11.1.4. Tristate Gates

Tristate gates can output three states: logic 0, logic 1, and high-impedance (Z).

1. BUFIF1 (Buffer if 1)

Output follows input when control is 1, otherwise high-impedance.

Truth Table:

Syntax:

bufif1 instance_name (output, input, control);

Example:

Verilog

2. BUFIF0 (Buffer if 0)

Output follows input when control is 0, otherwise high-impedance.

Truth Table:

Syntax:

bufif0 instance_name (output, input, control);

Example:

Verilog

3. NOTIF1 (Inverter if 1)

Inverts input when control is 1, otherwise high-impedance.

Truth Table:

Syntax:

notif1 instance_name (output, input, control);

4. NOTIF0 (Inverter if 0)

Inverts input when control is 0, otherwise high-impedance.

Truth Table:

Syntax:

notif0 instance_name (output, input, control);

11.1.5. Bidirectional Bus Example

Verilog

11.1.6. Gate Arrays and Vectors

Verilog allows instantiating multiple gates in a single statement.

Single Statement Multiple Instances

Verilog

Equivalent to:

and and_array0 (and_out[0], a[0], b[0]);

and and_array1 (and_out[1], a[1], b[1]);

and and_array2 (and_out[2], a[2], b[2]);

and and_array3 (and_out[3], a[3], b[3]);

Inverter Array Example

Verilog

11.1.7. Best Practices

1. Always Use Instance Names

Verilog

2. Use Appropriate Gate Types

Verilog

3. Document Gate Functions

Verilog

4. Use Gate Arrays for Repetitive Logic

Verilog

5. Handle Tristate Carefully

Verilog

6. Use Meaningful Wire Names

Verilog

11.1.8. Practical Examples

Example 1: 4-bit Parity Generator

Verilog

Example 2: Priority Encoder (4-to-2)

Verilog

Example 3: 1-bit Comparator

Verilog

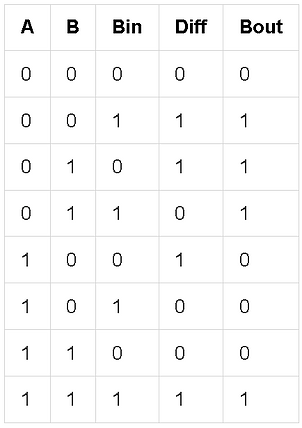

Example 4: Full Subtractor

Truth Table:

Verilog

Example 5: SR Latch using NOR Gates

Verilog

Example 6: D Latch using Gates

Verilog

Example 7: 8-bit Bus Transceiver

Verilog