Introduction(परिचय)

किसी भी डिजिटल सिस्टम के निर्माण की पहली प्रक्रिया होती है उसकी स्पेसिफिकेशन लिखना। ये स्पेसिफिकेशन ग्राहक की ज़रूरतों से बनते हैं और मार्केटिंग टीम के माध्यम से ASIC कंपनियों तक पहुँचते हैं।

इसके बाद सिस्टम की ब्लॉक लेवल डिजाइन बनाई जाती है और अंत में उसे RTL (Register Transfer Level) में कोडिंग करके लागू किया जाता है। यह RTL कोडिंग VHDL, Verilog या SystemVerilog किसी भी भाषा में की जा सकती है।

पहले के ज़माने में synthesis और simulation टूल उपलब्ध नहीं थे, इसलिए डिज़ाइन को कागज़ पर ही verify करना पड़ता था। लेकिन आजकल EDA (Electronic Design Automation) टूल्स की वजह से यह काम बहुत तेज़ और आसान हो गया है।

-

Synthesis tools: Quartus (Intel), Vivado (Xilinx)

-

Simulation tools: Questa (Siemens), Xcelium (Cadence)

इन टूल्स ने synthesis और simulation के समय को काफी कम कर दिया है।

VHDL एक disciplined और strongly typed language है, जिसे मूल रूप से U.S. Department of Defense के लिए बनाया गया था और इसका syntax ADA programming language से प्रेरित है।

वहीं, Verilog को C-like syntax के साथ डिज़ाइन किया गया, ताकि इंजीनियर्स इसे आसानी से और जल्दी सीख सकें।

आज भी अलग-अलग क्षेत्रों में अलग-अलग पसंद है:

-

यूरोप → VHDL को अधिकतर prefer किया जाता है

-

Defense और Aerospace कंपनियाँ → VHDL पर भरोसा करती हैं क्योंकि यह ज्यादा structured और disciplined है

VHDL अपनी खुद की एक सख्त संरचना (जैसे Entity, Architecture, Records, Libraries) लागू करता है। जब तक सभी आवश्यक libraries शामिल न हों, synthesis नहीं हो सकती। इससे डिज़ाइन में अनुशासन, स्पष्टता और भरोसेमंदी बनी रहती है।

जब Verilog है तो VHDL क्यों?

सोचिए, हमारे दैनिक जीवन में कितने ही सिस्टम होते हैं जो इनपुट लेते हैं और हमें वांछित आउटपुट देते हैं।

उदाहरण के लिए, एक टीवी को लीजिए: जब हम रिमोट का वॉल्यूम अप/डाउन बटन दबाते हैं तो आउटपुट के रूप में टीवी की आवाज़ बढ़ या घट जाती है।

यहाँ:

-

इनपुट = रिमोट से भेजा गया IR कमांड

-

आउटपुट = स्पीकर का वॉल्यूम (dB में)

-

सिस्टम डिज़ाइन = वह आंतरिक लॉजिक जो इनपुट को प्रोसेस करता है और स्पीकर की पावर को नियंत्रित करता है ताकि आवाज़ बढ़ या घट सके।

इस साधारण उदाहरण से आप आसानी से समझ सकते हैं कि —

हर डिजिटल सिस्टम इनपुट लेता है और आउटपुट देता है जो हमारी आवश्यकता (स्पेसिफिकेशन) के अनुसार होता है।

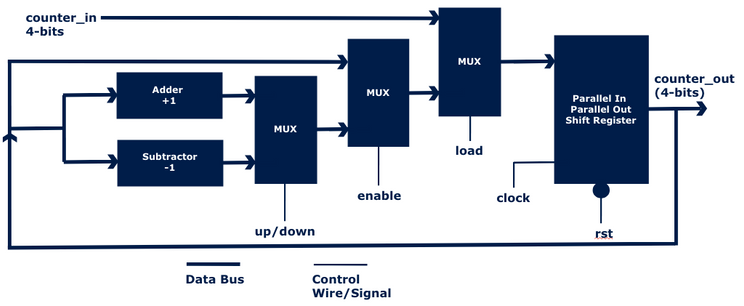

अब चलिए डिजिटल डिज़ाइन का एक क्लासिक उदाहरण लेते हैं — अप/डाउन काउंटर (Up/Down Counter)।

इसे केवल किताब से रटने की बजाय हम इसे तार्किक ढंग से समझते हैं।

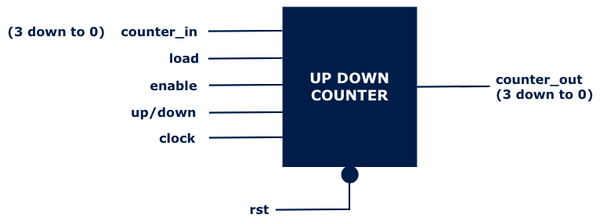

एक काउंटर के सामान्य इनपुट/आउटपुट सिग्नल होते हैं:

-

clk (क्लॉक)

-

rst (रीसेट)

-

counter_in (लोड करने के लिए इनपुट डेटा)

-

load (कंट्रोल सिग्नल जिससे counter_in लोड होता है)

-

enable (गिनती को सक्रिय करने के लिए)

-

counter_out (काउंटर का आउटपुट मान)

मूलभूत अवधारणाएँ (Core Concepts)

RTL Code

VHDL

LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

USE IEEE.numeric_std.all;

ENTITY counter IS

PORT (

clock : IN std_logic;

rst : IN std_logic;

ENABLE : IN std_logic;

LOAD : IN std_logic;

UP_DOWN : IN std_logic;

counter_in : IN std_logic_vector(3 DOWNTO 0);

counter_out : OUT std_logic_vector(3 DOWNTO 0)

);

END counter;

ARCHITECTURE behavioral OF counter IS

SIGNAL counter_out_tmp : unsigned(3 DOWNTO 0); -- unsigned type for arithmetic

BEGIN

counter_proc : PROCESS (rst, clock)

BEGIN

IF (rst = '0') THEN

counter_out_tmp <= (OTHERS => '0');

ELSIF rising_edge(clock) THEN

IF (LOAD = '1') THEN

counter_out_tmp <= unsigned(counter_in);

ELSIF (ENABLE = '1') THEN

IF (UP_DOWN = '1') THEN

counter_out_tmp <= counter_out_tmp + 1;

ELSE

counter_out_tmp <= counter_out_tmp - 1;

END IF;

END IF;

END IF;

END PROCESS;

counter_out <= std_logic_vector(counter_out_tmp); -- convert back

END behavioral;

VIVADO ELABORATION DIAGRAM

एडवांस्ड लेक्चर्स में हम विस्तार से देखेंगे कि RTL को कैसे डिज़ाइन किया गया और कैसे उसे सिंथेसाइज़ किया गया।

VIVADO synthesis

SIMULATION

-

संचार प्रणालियाँ (Communication systems) → जैसे modems, encoders

-

ऑटोमोबाइल सुरक्षा प्रणालियाँ (Automotive safety systems) → जैसे airbag controllers

-

CPU और DSP डिज़ाइन (CPU & DSP design)

-

अंतरिक्ष और रक्षा उपकरण (Space and defense hardware)

अनुप्रयोग (Applications)

VHDL का भविष्य (Future of VHDL)

-

VHDL-2008 → उन्नत (enhanced) सिंटैक्स, fixed और floating-point सपोर्ट, और बेहतर modeling features.

-

यह अभी भी Verilog और SystemVerilog के साथ प्रासंगिक (relevant) है, क्योंकि यह बहुत मजबूत (robust) भाषा है।