14.7. Introduction to Generate Blocks

Generate blocks are powerful Verilog constructs that allow conditional and iterative instantiation of hardware modules, variables, and continuous assignments at elaboration time. Unlike procedural loops, generate constructs are FULLY SYNTHESIZABLE and create actual hardware instances.

What are Generate Blocks?

Generate blocks enable parametric and configurable hardware design by allowing you to:

-

Instantiate multiple module instances using loops

-

Conditionally include or exclude hardware based on parameters

-

Create arrays of gates, flip-flops, or modules

-

Build scalable and reusable designs

-

Reduce code duplication

Generate vs Regular Loops

.png)

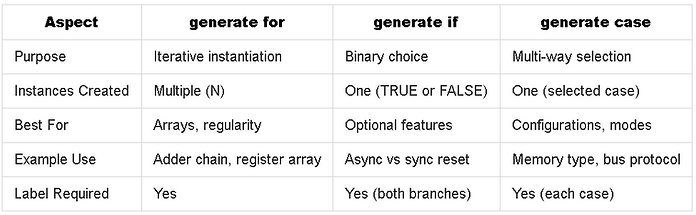

Types of Generate Constructs

-

generate for - Iterative instantiation (arrays of instances)

-

generate if - Conditional instantiation (include/exclude hardware)

-

generate case - Multi-way conditional instantiation (select one of many)

Critical: Elaboration Time Execution

✓ KEY ADVANTAGE: Generate blocks execute at ELABORATION TIME (before simulation). This means they create actual hardware structures that are fully synthesizable. Parameters and constants are evaluated to determine what hardware to instantiate.

14.7.1. Generate For

14.7.2. Generate If

14.7.3. Generate Case

14.7.4. Advanced Generate Techniques

Comparison of Generate Types

.png)

When to Use Each Type

-

Use generate for: Creating regular arrays, chains, or multiple similar instances

-

Use generate if: Binary choices, optional features, enable/disable blocks

-

Use generate case: Multiple configurations, selecting among several alternatives